集成電路設(shè)計(jì)領(lǐng)域文獻(xiàn)綜述 技術(shù)演進(jìn)、前沿挑戰(zhàn)與未來(lái)展望

集成電路設(shè)計(jì)作為現(xiàn)代電子工業(yè)的基石,其發(fā)展深刻影響著信息技術(shù)、人工智能、物聯(lián)網(wǎng)等關(guān)鍵領(lǐng)域的進(jìn)步。本文基于對(duì)近十年相關(guān)文獻(xiàn)的系統(tǒng)梳理,從技術(shù)演進(jìn)、設(shè)計(jì)方法、關(guān)鍵挑戰(zhàn)及未來(lái)趨勢(shì)四個(gè)方面展開(kāi)綜述。

一、技術(shù)演進(jìn)與設(shè)計(jì)范式的轉(zhuǎn)變

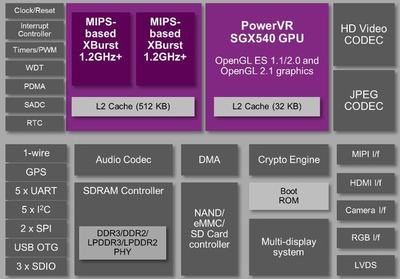

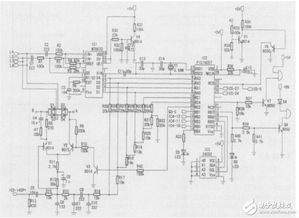

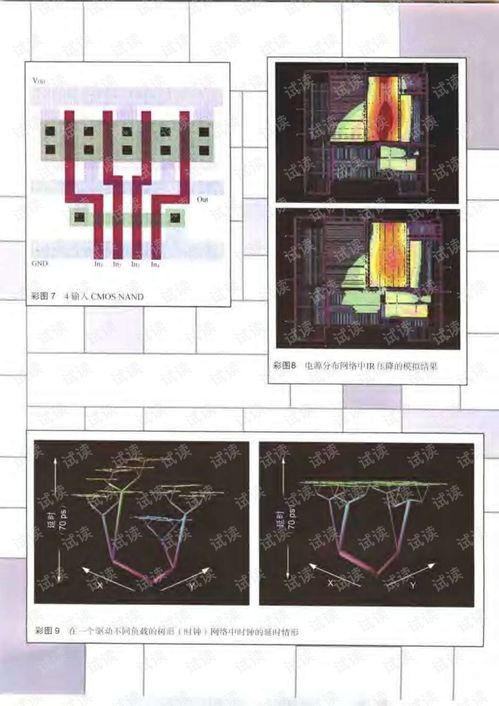

早期集成電路設(shè)計(jì)以全定制和標(biāo)準(zhǔn)單元為主,強(qiáng)調(diào)性能與面積的優(yōu)化。隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度,設(shè)計(jì)復(fù)雜度呈指數(shù)級(jí)增長(zhǎng),電子設(shè)計(jì)自動(dòng)化(EDA)工具成為不可或缺的支撐。多物理場(chǎng)耦合、信號(hào)完整性及低功耗設(shè)計(jì)逐漸成為核心議題。異構(gòu)集成、芯粒(Chiplet)技術(shù)和硅光集成等新興范式,通過(guò)模塊化設(shè)計(jì)打破了傳統(tǒng)單芯片的性能瓶頸,為后摩爾定律時(shí)代提供了可行路徑。

二、設(shè)計(jì)方法學(xué)的前沿發(fā)展

在邏輯與物理設(shè)計(jì)層面,高層次綜合(HLS)與基于機(jī)器學(xué)習(xí)的設(shè)計(jì)優(yōu)化方法顯著提升了設(shè)計(jì)效率。例如,強(qiáng)化學(xué)習(xí)被應(yīng)用于布局布線優(yōu)化,生成對(duì)抗網(wǎng)絡(luò)(GAN)用于快速電路仿真模型構(gòu)建。面向特定領(lǐng)域架構(gòu)(DSA)的設(shè)計(jì),如神經(jīng)網(wǎng)絡(luò)加速器和量子計(jì)算控制芯片,凸顯了軟硬件協(xié)同優(yōu)化的重要性。開(kāi)源EDA工具鏈(如OpenROAD)的興起,進(jìn)一步降低了設(shè)計(jì)門(mén)檻,促進(jìn)了產(chǎn)學(xué)研協(xié)作。

三、當(dāng)前面臨的關(guān)鍵挑戰(zhàn)

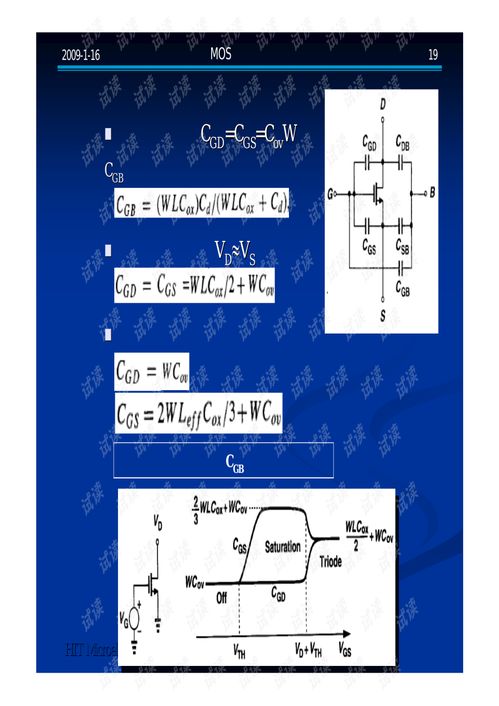

盡管技術(shù)不斷突破,集成電路設(shè)計(jì)仍面臨多重挑戰(zhàn):工藝微縮帶來(lái)的短溝道效應(yīng)、熱載流子退化等物理限制加劇了可靠性問(wèn)題;設(shè)計(jì)周期與成本居高不下,尤其是在3D集成和先進(jìn)封裝中;安全性與知識(shí)產(chǎn)權(quán)保護(hù)成為重要關(guān)切,硬件木馬與側(cè)信道攻擊防護(hù)需求迫切;可持續(xù)發(fā)展要求推動(dòng)低功耗與碳足跡優(yōu)化成為新的設(shè)計(jì)指標(biāo)。

四、未來(lái)趨勢(shì)與研究方向

未來(lái)集成電路設(shè)計(jì)將呈現(xiàn)多維度融合特征:一方面,與新型計(jì)算范式(如存算一體、 neuromorphic computing)結(jié)合,探索非馮·諾依曼架構(gòu);另一方面,依托硅基光子學(xué)與寬禁帶半導(dǎo)體材料,拓展高頻、高功率應(yīng)用場(chǎng)景。設(shè)計(jì)方法學(xué)將更依賴(lài)數(shù)據(jù)驅(qū)動(dòng)與人工智能,實(shí)現(xiàn)自主設(shè)計(jì)閉環(huán)。隨著量子芯片、生物集成電路等跨學(xué)科領(lǐng)域的興起,集成電路設(shè)計(jì)的邊界將持續(xù)擴(kuò)展。

集成電路設(shè)計(jì)正經(jīng)歷從傳統(tǒng)范式向智能、異構(gòu)、可持續(xù)方向的深刻變革。未來(lái)研究需聚焦于跨尺度建模、設(shè)計(jì)自動(dòng)化智能化、及多學(xué)科交叉創(chuàng)新,以應(yīng)對(duì)日益復(fù)雜的技術(shù)與社會(huì)需求。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.jjmake.cn/product/35.html

更新時(shí)間:2026-01-13 17:52:48