鰭式場效晶體管(FinFET)集成電路設(shè)計與測試技術(shù)詳解

隨著半導(dǎo)體工藝制程的不斷微縮,鰭式場效晶體管(FinFET)已成為現(xiàn)代集成電路設(shè)計的主流技術(shù)。本文將從FinFET的基本原理、設(shè)計流程、電路圖解析及測試方法等方面進行詳細(xì)闡述。

一、FinFET技術(shù)原理與優(yōu)勢

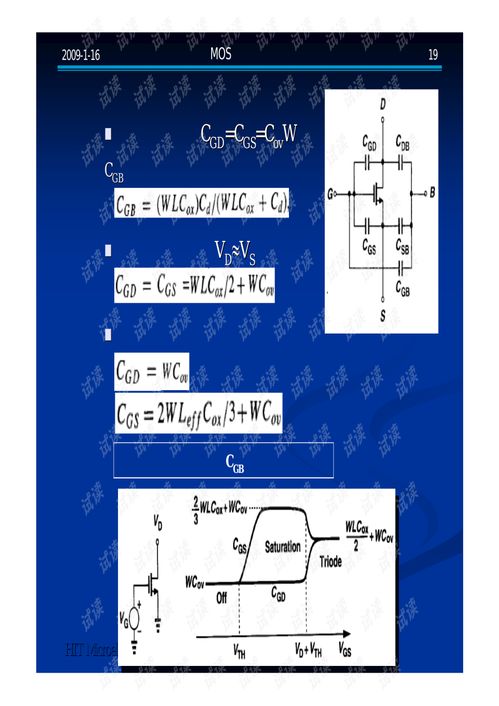

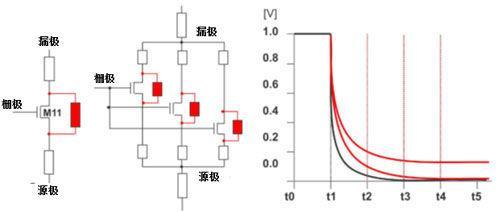

鰭式場效晶體管是一種三維晶體管結(jié)構(gòu),其柵極從三面包裹鰭形溝道,相比傳統(tǒng)的平面MOSFET具有以下顯著優(yōu)勢:

- 更好的柵極控制能力:三面包裹結(jié)構(gòu)增強了柵極對溝道的控制,有效抑制短溝道效應(yīng)

- 更低的工作電壓:可在更低的電源電壓下工作,大幅降低功耗

- 更高的開關(guān)速度:載流子遷移率提升,開關(guān)特性更優(yōu)

- 更高的集成密度:三維結(jié)構(gòu)允許在單位面積內(nèi)集成更多晶體管

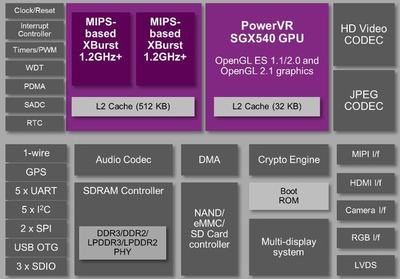

二、FinFET集成電路設(shè)計流程

- 架構(gòu)設(shè)計階段

- 確定電路功能規(guī)格和性能指標(biāo)

- 選擇適當(dāng)?shù)墓に嚬?jié)點(如7nm、5nm等)

- 制定系統(tǒng)架構(gòu)方案

- 電路設(shè)計階段

- 使用硬件描述語言(Verilog/VHDL)進行RTL設(shè)計

- FinFET器件建模與參數(shù)提取

- 邏輯綜合與時序分析

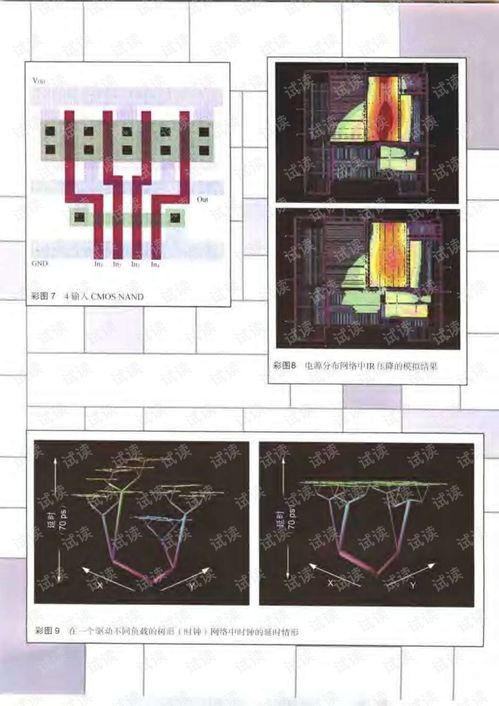

- 物理設(shè)計階段

- 布局規(guī)劃與電源網(wǎng)絡(luò)設(shè)計

- 標(biāo)準(zhǔn)單元布局與FinFET特定布局規(guī)則

- 時鐘樹綜合與時序優(yōu)化

- 布線設(shè)計與設(shè)計規(guī)則檢查

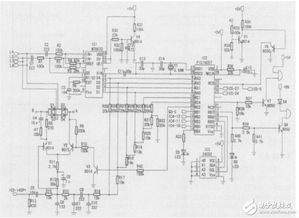

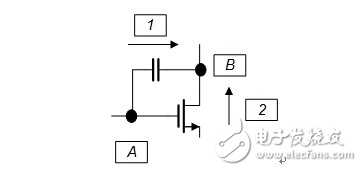

三、典型FinFET電路圖解析

以一個簡單的FinFET反相器為例:

電路結(jié)構(gòu)包括:

- PMOS FinFET:源極接VDD,漏極接輸出

- NMOS FinFET:源極接VSS,漏極接輸出

- 柵極:PMOS和NMOS柵極共同連接輸入信號

工作特性:

- 輸入低電平時:PMOS導(dǎo)通,NMOS截止,輸出高電平

- 輸入高電平時:PMOS截止,NMOS導(dǎo)通,輸出低電平

- 由于FinFET的優(yōu)異開關(guān)特性,該反相器具有更快的開關(guān)速度和更低的靜態(tài)功耗

四、FinFET集成電路測試技術(shù)

- 直流參數(shù)測試

- 閾值電壓測量

- 導(dǎo)通電阻測試

- 漏電流測試

- 交流參數(shù)測試

- 開關(guān)速度測試

- 傳輸延遲測量

- 功耗測試

- 可靠性測試

- 熱載流子注入測試

- 偏置溫度不穩(wěn)定性測試

- 電遷移測試

- 功能測試

- 靜態(tài)功能驗證

- 動態(tài)功能測試

- 邊界掃描測試

五、設(shè)計挑戰(zhàn)與解決方案

- 工藝變化影響

- 采用統(tǒng)計靜態(tài)時序分析

- 實施工藝角分析和蒙特卡洛仿真

- 功耗管理

- 多閾值電壓技術(shù)

- 電源門控技術(shù)

- 動態(tài)電壓頻率調(diào)節(jié)

- 熱管理

- 熱敏感布局設(shè)計

- 散熱結(jié)構(gòu)優(yōu)化

- 溫度感知時序分析

FinFET技術(shù)將繼續(xù)推動集成電路向更高性能、更低功耗的方向發(fā)展。設(shè)計人員需要深入理解FinFET特性,采用先進的設(shè)計方法和測試技術(shù),才能充分發(fā)揮其技術(shù)優(yōu)勢,實現(xiàn)高質(zhì)量的集成電路產(chǎn)品。

如若轉(zhuǎn)載,請注明出處:http://www.jjmake.cn/product/38.html

更新時間:2026-01-13 07:10:46